# PLANEJAMENTO DA ESTRATÉGIA DE INSPEÇÃO E TESTE EM MONTAGEM DE PLACAS ELETRÔNICAS

UMA ABORDAGEM UTILIZANDO ALGORITMOS GENÉTICOS

MVI

SPI

AOI

AXI

MDA

ICT

BST

FT

1

0

1

0

0

1

0

1

MARCOS MARINOVIC DORO

Atena

Editora

Ano 2023

# PLANEJAMENTO DA ESTRATÉGIA DE INSPEÇÃO E TESTE EM MONTAGEM DE PLACAS ELETRÔNICAS

UMA ABORDAGEM UTILIZANDO ALGORITMOS GENÉTICOS

MVI

SPI

AOI

AXI

ICT

FT

BST

FT

1

0

1

0

0

1

0

1

MARCOS MARINOVIC DORO

Atena

Editora

Ano 2023

|                                          |                                      |

|------------------------------------------|--------------------------------------|

| <b>Editora chefe</b>                     |                                      |

| Profª Drª Antonella Carvalho de Oliveira |                                      |

| <b>Editora executiva</b>                 |                                      |

| Natalia Oliveira                         |                                      |

| <b>Assistente editorial</b>              |                                      |

| Flávia Roberta Barão                     |                                      |

| <b>Bibliotecária</b>                     |                                      |

| Janaina Ramos                            |                                      |

| <b>Projeto gráfico</b>                   |                                      |

| Camila Alves de Cremo                    | 2024 by Atena Editora                |

| Ellen Andressa Kubisty                   | Copyright © Atena Editora            |

| Luiza Alves Batista                      | Copyright do texto © 2024 Os autores |

| Nataly Evilin Gayde                      | Copyright da edição © 2024 Atena     |

| Thamires Camili Gayde                    | Editora                              |

| <b>Imagens da capa</b>                   | Direitos para esta edição cedidos à  |

| iStock                                   | Atena Editora pelos autores.         |

| <b>Edição de arte</b>                    | Open access publication by Atena     |

| Luiza Alves Batista                      | Editora                              |

Todo o conteúdo deste livro está licenciado sob uma Licença de Atribuição Creative Commons. Atribuição-Não-Comercial-NãoDerivativos 4.0 Internacional (CC BY-NC-ND 4.0).

O conteúdo dos artigos e seus dados em sua forma, correção e confiabilidade são de responsabilidade exclusiva dos autores, inclusive não representam necessariamente a posição oficial da Atena Editora. Permitido o download da obra e o compartilhamento desde que sejam atribuídos créditos aos autores, mas sem a possibilidade de alterá-la de nenhuma forma ou utilizá-la para fins comerciais.

Todos os manuscritos foram previamente submetidos à avaliação cega pelos pares, membros do Conselho Editorial desta Editora, tendo sido aprovados para a publicação com base em critérios de neutralidade e imparcialidade acadêmica.

A Atena Editora é comprometida em garantir a integridade editorial em todas as etapas do processo de publicação, evitando plágio, dados ou resultados fraudulentos e impedindo que interesses financeiros comprometam os padrões éticos da publicação. Situações suspeitas de má conduta científica serão investigadas sob o mais alto padrão de rigor acadêmico e ético.

#### **Conselho Editorial**

#### **Ciências Exatas e da Terra e Engenharias**

Prof. Dr. Adélio Alcino Sampaio Castro Machado – Universidade do Porto

Profª Drª Alana Maria Cerqueira de Oliveira – Instituto Federal do Acre

Profª Drª Ana Grasielle Dionísio Corrêa – Universidade Presbiteriana Mackenzie

Profª Drª Ana Paula Florêncio Aires – Universidade de Trás-os-Montes e Alto Douro

Prof. Dr. Carlos Eduardo Sanches de Andrade – Universidade Federal de Goiás

Profª Drª Carmen Lúcia Voigt – Universidade Norte do Paraná

- Prof. Dr. Cleiseano Emanuel da Silva Paniagua – Instituto Federal de Educação, Ciência e Tecnologia de Goiás

Prof. Dr. Douglas Gonçalves da Silva – Universidade Estadual do Sudoeste da Bahia

Prof. Dr. Eloi Rufato Junior – Universidade Tecnológica Federal do Paraná

Prof<sup>a</sup> Dr<sup>a</sup> Érica de Melo Azevedo – Instituto Federal do Rio de Janeiro

Prof. Dr. Fabrício Menezes Ramos – Instituto Federal do Pará

Prof. Dr. Fabrício Moraes de Almeida – Universidade Federal de Rondônia

Prof<sup>a</sup> Dr<sup>a</sup> Glécilla Colombelli de Souza Nunes – Universidade Estadual de Maringá

Prof<sup>a</sup> Dr<sup>a</sup> Iara Margolis Ribeiro – Universidade Federal de Pernambuco

Prof<sup>a</sup> Dra. Jéssica Verger Nardeli – Universidade Estadual Paulista Júlio de Mesquita Filho

Prof. Dr. Juliano Bitencourt Campos – Universidade do Extremo Sul Catarinense

Prof. Dr. Juliano Carlo Rufino de Freitas – Universidade Federal de Campina Grande

Prof<sup>a</sup> Dr<sup>a</sup> Luciana do Nascimento Mendes – Instituto Federal de Educação, Ciência e Tecnologia do Rio Grande do Norte

Prof. Dr. Marcelo Marques – Universidade Estadual de Maringá

Prof. Dr. Marco Aurélio Kistemann Junior – Universidade Federal de Juiz de Fora

Prof<sup>a</sup> Dr<sup>a</sup> Maria José de Holanda Leite – Universidade Federal de Alagoas

Prof. Dr. Miguel Adriano Inácio – Instituto Nacional de Pesquisas Espaciais

Prof. Dr. Milson dos Santos Barbosa – Universidade Tiradentes

Prof<sup>a</sup> Dr<sup>a</sup> Natiéli Piovesan – Instituto Federal do Rio Grande do Norte

Prof<sup>a</sup> Dr<sup>a</sup> Neiva Maria de Almeida – Universidade Federal da Paraíba

Prof. Dr. Nilzo Ivo Ladwig – Universidade do Extremo Sul Catarinense

Prof<sup>a</sup> Dr<sup>a</sup> Priscila Tessmer Scaglioni – Universidade Federal de Pelotas

Prof<sup>a</sup> Dr Ramiro Picoli Nippes – Universidade Estadual de Maringá

Prof<sup>a</sup> Dr<sup>a</sup> Regina Célia da Silva Barros Allil – Universidade Federal do Rio de Janeiro

Prof. Dr. Sidney Gonçalo de Lima – Universidade Federal do Piauí

Prof. Dr. Takeshy Tachizawa – Faculdade de Campo Limpo Paulista

**Planejamento da estratégia de inspeção e teste em montagem de placas eletrônicas - Uma abordagem utilizando algoritmos genéticos**

**Diagramação:** Ellen Andressa Kubisty

**Correção:** Yaiddy Paola Martinez

**Indexação:** Amanda Kelly da Costa Veiga

**Revisão:** Os autores

**Autor:** Marcos Marinovic Doro

| Dados Internacionais de Catalogação na Publicação (CIP)                                                                                                                                                                                                                                                                                                                                                                                                               |                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| D715                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Doro, Marcos Marinovic |

| <p>Planejamento da estratégia de inspeção e teste em montagem de placas eletrônicas - Uma abordagem utilizando algoritmos genéticos / Marcos Marinovic Doro. – Ponta Grossa - PR: Atena, 2024.</p> <p>Formato: PDF<br/>Requisitos de sistema: Adobe Acrobat Reader<br/>Modo de acesso: World Wide Web<br/>Inclui bibliografia<br/>ISBN 978-65-258-2123-8<br/>DOI: <a href="https://doi.org/10.22533/at.ed.238240501">https://doi.org/10.22533/at.ed.238240501</a></p> |                        |

| <p>I. Algoritmos de otimização. I. Doro, Marcos Marinovic.<br/>II. Título.<br/>CDD 005.74</p>                                                                                                                                                                                                                                                                                                                                                                         |                        |

| <p>Elaborado por Bibliotecária Janaina Ramos – CRB-8/9166</p>                                                                                                                                                                                                                                                                                                                                                                                                         |                        |

## **DECLARAÇÃO DOS AUTORES**

Os autores desta obra: 1. Atestam não possuir qualquer interesse comercial que constitua um conflito de interesses em relação ao artigo científico publicado; 2. Declaram que participaram ativamente da construção dos respectivos manuscritos, preferencialmente na: a) Concepção do estudo, e/ou aquisição de dados, e/ou análise e interpretação de dados; b) Elaboração do artigo ou revisão com vistas a tornar o material intelectualmente relevante; c) Aprovação final do manuscrito para submissão.; 3. Certificam que os artigos científicos publicados estão completamente isentos de dados e/ou resultados fraudulentos; 4. Confirmam a citação e a referência correta de todos os dados e de interpretações de dados de outras pesquisas; 5. Reconhecem terem informado todas as fontes de financiamento recebidas para a consecução da pesquisa; 6. Autorizam a edição da obra, que incluem os registros de ficha catalográfica, ISBN, DOI e demais indexadores, projeto visual e criação de capa, diagramação de miolo, assim como lançamento e divulgação da mesma conforme critérios da Atena Editora.

## **DECLARAÇÃO DA EDITORA**

A Atena Editora declara, para os devidos fins de direito, que: 1. A presente publicação constitui apenas transferência temporária dos direitos autorais, direito sobre a publicação, inclusive não constitui responsabilidade solidária na criação dos manuscritos publicados, nos termos previstos na Lei sobre direitos autorais (Lei 9610/98), no art. 184 do Código Penal e no art. 927 do Código Civil; 2. Autoriza e incentiva os autores a assinarem contratos com repositórios institucionais, com fins exclusivos de divulgação da obra, desde que com o devido reconhecimento de autoria e edição e sem qualquer finalidade comercial; 3. Todos os e-book são *open access*, *desta forma* não os comercializa em seu site, sites parceiros, plataformas de e-commerce, ou qualquer outro meio virtual ou físico, portanto, está isenta de repasses de direitos autorais aos autores; 4. Todos os membros do conselho editorial são doutores e vinculados a instituições de ensino superior públicas, conforme recomendação da CAPES para obtenção do Qualis livro; 5. Não cede, comercializa ou autoriza a utilização dos nomes e e-mails dos autores, bem como nenhum outro dado dos mesmos, para qualquer finalidade que não o escopo da divulgação desta obra.

## DEDICATÓRIA

Este livro é dedicado a toda minha família,

em especial a minha esposa Larissa e

minha filha Maria.

Atualmente no mercado da manufatura eletrônica existe uma grande pressão para reduzir custos, aumentar a qualidade e encurtar o tempo de inserção do produto no mercado. Neste contexto, o adequado planejamento de qualidade gera um alto ganho no ambiente competitivo, sendo um meio de alavancar a eficiência e a qualidade dos processos de uma empresa. No entanto, os planejadores da qualidade de hoje possuem significativamente muito mais desafios do que os de apenas alguns anos atrás. A complexidade das placas eletrônicas está aumentando, com mais componentes, mais juntas de solda, densidades mais elevadas, novas tecnologias de encapsulamentos de componentes, entre outros. Ao mesmo tempo, existem mais alternativas de equipamentos de inspeção e teste com novas tecnologias.

O nível de rendimento ou defeitos esperado na montagem de uma determinada placa eletrônica depende de vários fatores, dentre quais destacam-se: o projeto da placa eletrônica, os tipos de componentes utilizados, o número de componentes e juntas de solda, os processos executados, bem como a qualidade destes processos. Quanto maior for o número de componentes, juntas e processos, mais oportunidades de defeitos são criadas, o que leva a um rendimento mais baixo para um determinado nível defeito histórico. Em outras palavras, durante a produção de um lote placas eletrônicas muito complexas, com muitas oportunidades de defeitos, é esperado ser contabilizado um número de defeitos muito maior do que um lote de produção de placas eletrônicas simples.

Desta forma, se o número de defeitos contabilizados durante a produção não é fixo para todos os tipos de placa eletrônica, deve-se planejar as inspeções e os testes de forma eficaz e de forma particular para cada modelo de placas eletrônica. O planejamento das inspeções e dos testes tem por finalidade prover informações confiáveis referentes ao atendimento dos requisitos da qualidade dos produtos e dos processos. Ele deve garantir primordialmente que as inspeções e os testes sejam realizados de forma suficientemente econômica e ao mesmo tempo garantir a maior cobertura de defeitos possível.

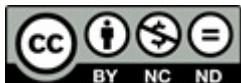

O processo de montagem de placas eletrônicas possui uma multiplicidade de questões a serem consideradas durante o planejamento das inspeções e testes. Existe uma variedade de técnicas de inspeção e testes disponíveis, dentre estas se destacam: Inspeção Óptica Automática (AOI), Inspeção de Pasta de Solda (SPI), Inspeção Raios-X Automática (AXI), Teste *In-Circuit* (ICT), Teste *Boundary Scan* –JTAG, entre outras. No entanto, não existe uma única técnica que sane todos os desafios e identifique todos os defeitos gerados durante a montagem, cada uma tem suas próprias vantagens e desvantagens, sendo necessário avaliar cada possível solução dentre as diferentes combinações

disponíveis. O diagrama de Venn na Figura 1 mostra a cobertura de defeitos para algumas das principais técnicas de inspeção e teste.

Figura 1 - Cobertura de defeitos das principais técnicas de inspeção e teste empregadas na montagem de placas eletrônicas (adaptado de LOTZ, 2009)

Cada uma destas tecnologias possui sua própria cobertura de defeitos e características de desempenho, o planejador deve avaliar seu próprio espectro de defeitos e seus objetivos de desempenho a fim de optar por uma determinada técnica. O planejador deverá balancear os conflitos entre custos operacionais, custos de capital, cobertura de defeitos, rendimento e diagnóstico. A eficácia de cada técnica revela as capacidades relativas dos diferentes tipos de equipamentos de inspeção de teste e o posicionamento ideal dos mesmos na linha de montagem.

Como se pode observar, o planejamento das inspeções e dos testes é uma etapa crítica de ser realizada no processo de montagem de placas eletrônicas, devido à complexidade de informações para estabelecer a melhor escolha das diferentes técnicas de inspeção e testes para a variedade de produtos. Por sua vez, o planejamento passou a ser um dos objetos de estudo na área de Inteligência Artificial (IA). O problema de planejamento em IA pode ser definido informalmente como o processo de se estabelecer uma sequência de ações que levam ao resultado desejado.

Atualmente a área de planejamento em IA está subdividida em dois segmentos: o planejamento clássico e o planejamento não clássico. No primeiro, ocorre em ambientes completamente observáveis, determinísticos,

finitos, estáticos e discretos. Por sua vez, no planejamento não clássico o agente depara-se com situações imprevisíveis, cujo grau de certeza da ação nem sempre é absoluto. O planejamento em IA se interessa por abordagens gerais independente do domínio para o planejamento. Desta forma, ele pode ser empregado em diversas áreas, tais como: robótica, logística, processos industriais, problemas de escalonamento, jogos de estratégia, composição de serviços-web, planejamento para recuperação de informação, entre outros. Geralmente os planos são gerados para otimizar algum critério: custo, tempo, qualidade, etc.

Em geral, existem diversas maneiras de se representar um problema de planejamento. As primeiras abordagens para o problema de planejamento têm suas raízes na década de 60, quando o planejamento automático era feito como prova de teoremas em lógica de primeira ordem como representação. Pelo fato de tratar lidar de problemas complexos, resolveu-se na época estabelecer um formalismo esta lógica, este sistema foi denominado de STRIPS (*Stanford Research Institute Problem Solver*). Esta solução agregava uma linguagem de representação simples e um algoritmo clássico de busca no espaço de estados. Por este motivo foi adotado como sistema padrão pela comunidade de planejamento e até hoje é a base dos principais planejadores modernos.

Com o passar dos anos, vários foram os trabalhos que direcionaram ao estudo e tratamento de problemas do planejamento, transformando-o numa área multidisciplinar e dinâmica. Com essa multidisciplinaridade, diversificaram-se os domínios e consequentemente ampliou-se a complexidade dos sistemas e surgiram novos métodos, entre eles os baseados em Funções Heurísticas, Redes de Petri, Satisfação de Restrições, Prova de teoremas, Algoritmos Genéticos, entre outros.

Em suma, o planejamento em IA é uma área de pesquisa que integra diversas áreas do conhecimento. O presente trabalho aplicou Algoritmos Genéticos como técnica de otimização para selecionar a melhor escolha em problemas de planejamento. Algoritmos Genéticos (AG) são modelos computacionais que imitam os mecanismos da evolução natural que podem ser usados para resolver problemas de busca e otimização, eles fazem parte da computação evolucionária, que é uma área em crescimento da IA. O tratamento de situações de planejamento a partir de AG se mostra bastante interessante no cenário atual da área, pois apresenta um grande espaço de busca, o que é uma característica dos problemas tratados de forma satisfatória por AG. Outro fator relevante é o relaxamento da restrição de otimização da solução, presente em vários planejadores atuais, o que facilita a busca pela solução no AG.

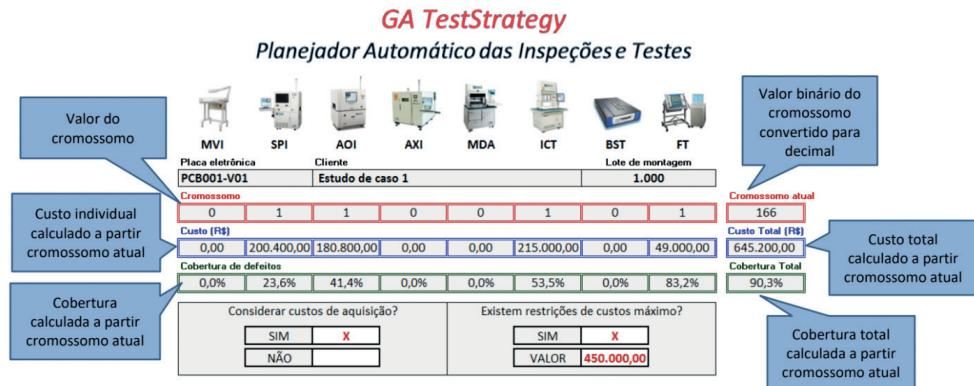

O presente trabalho aplicou Algoritmos Genéticos como técnica de otimização, o NSGA-II foi o algoritmo utilizado para resolução do problema de planejamento da inspeção e teste. Com esse propósito, empregou-se o software Microsoft Excel em conjunto com o componente *SolveXL* para executar as funções objetivo e as demais etapas correlacionadas ao Algoritmos Genéticos. Para a análise dos resultados, três modelos de placas eletrônicas de diferentes níveis de complexidades foram escolhidos.

Desta forma, conceitos importantes sobre as técnicas de inspeção e teste e a apresentação de uma ferramenta para auxiliar os planejadores da qualidade do processo de montagem de placas eletrônicas é o foco principal deste livro. Será apresentado detalhadamente a construção de um método capaz de gerar automaticamente a melhor estratégia de inspeção e teste a cada nova placa eletrônica introduzida na linha de montagem.

A seguir, no capítulo 1 são apresentadas as considerações mais relevantes para a definição da melhor estratégia de inspeção e teste para detectar os diferentes tipos de defeitos durante a montagem de uma placa eletrônica. No capítulo 2 é realizado um desenvolvimento descritivo e teórico de Algoritmos Genéticos. O capítulo 3 descreve um aplicativo idealizado voltado para a definição da estratégia de inspeção e teste no processo de montagem de placas eletrônicas. Finalmente no capítulo 4 são discutidos os resultados obtidos e apresentadas a considerações finais.

|                                                                                                         |           |

|---------------------------------------------------------------------------------------------------------|-----------|

| <b>PLANEJAMENTO DAS INSPEÇÕES E TESTES NO PROCESSO DE MONTAGEM DE PLACAS ELETRÔNICAS .....</b>          | <b>1</b>  |

| 1.1 Defeitos na montagem de placas eletrônicas .....                                                    | 1         |

| 1.2 Técnicas de inspeção e teste no processo de montagem de placas eletrônicas.....                     | 4         |

| 1.2.1 Inspeção .....                                                                                    | 4         |

| 1.2.2 Testes estruturais .....                                                                          | 8         |

| 1.2.3 Testes funcionais (FT).....                                                                       | 11        |

| 1.3 Estratégia de inspeção e teste .....                                                                | 13        |

| 1.3.1 Padrões de avaliação a cobertura de defeitos .....                                                | 16        |

| <b>ALGORITMOS GENÉTICOS COMO FERRAMENTA PARA O PLANEJAMENTO DA ESTRATÉGIA DE INSPEÇÃO E TESTE .....</b> | <b>18</b> |

| 2.1 Inicialização (Codificação).....                                                                    | 20        |

| 2.2 Avaliação (Função objetivo ou <i>fitness</i> ).....                                                 | 21        |

| 2.3 Seleção .....                                                                                       | 22        |

| 2.3.1 Seleção por torneio .....                                                                         | 23        |

| 2.3.2 Seleção uniforme.....                                                                             | 23        |

| 2.3.3 Seleção da roleta .....                                                                           | 23        |

| 2.3.4 Seleção por <i>ranking</i> .....                                                                  | 24        |

| 2.4 Cruzamento ( <i>Recombinação</i> ) .....                                                            | 24        |

| 2.4.1 Cruzamento em um ponto .....                                                                      | 24        |

| 2.4.2 Cruzamento multipontos .....                                                                      | 25        |

| 2.4.3 Cruzamento Uniforme .....                                                                         | 25        |

| 2.5 Mutação .....                                                                                       | 26        |

| 2.5.1 Mutação por inversão .....                                                                        | 26        |

| 2.5.2 Mutação Uniforme .....                                                                            | 26        |

| 2.5.3 Mutação Gaussiana.....                                                                            | 26        |

| 2.5.4 Mutação Creep.....                                                                                | 27        |

# SUMÁRIO

|                                                                                                                             |           |

|-----------------------------------------------------------------------------------------------------------------------------|-----------|

| 2.6 Finalização.....                                                                                                        | 27        |

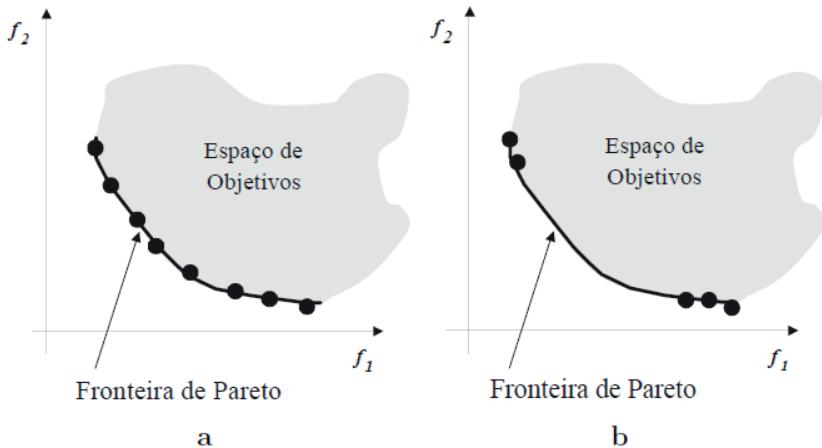

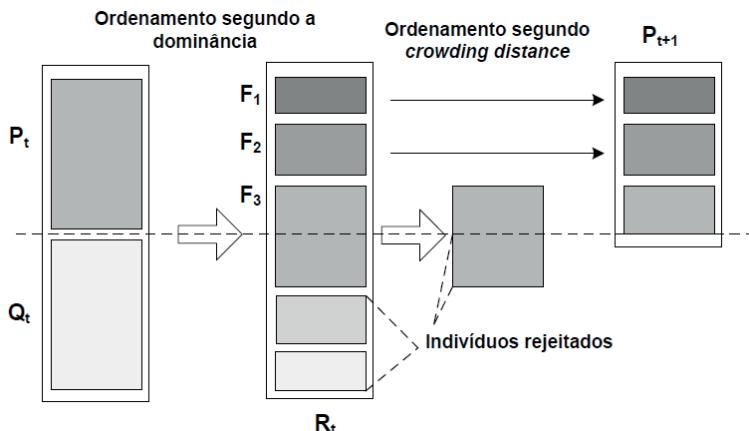

| 2.7 Algoritmos Genéticos Multi-Objetivos.....                                                                               | 27        |

| 2.7.1 NSGA-II: Non-dominated Sorting Genetic Algorithm .....                                                                | 30        |

| 2.8 Discussões de implementação.....                                                                                        | 31        |

| <b>APLICATIVO PARA O PLANEJAMENTO DA ESTRATÉGIA DE INSPEÇÕES E TESTES NO PROCESSO DE MONTAGEM DE PLACAS ELETRÔNICAS....</b> | <b>33</b> |

| 3.1 Estruturação do aplicativo .....                                                                                        | 34        |

| 3.1.1 Planilhas .....                                                                                                       | 34        |

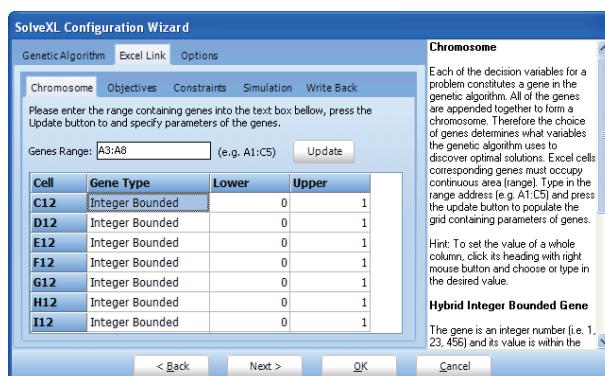

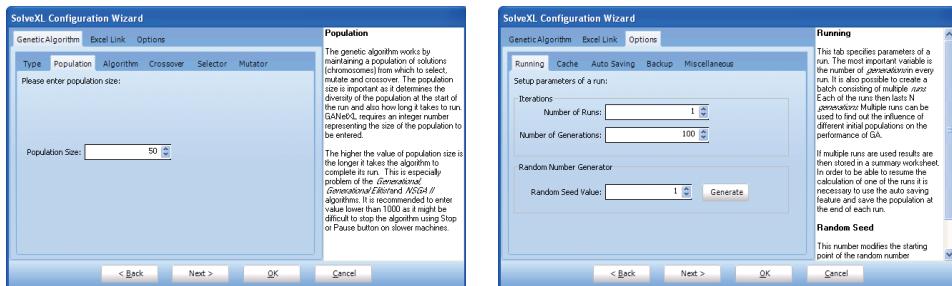

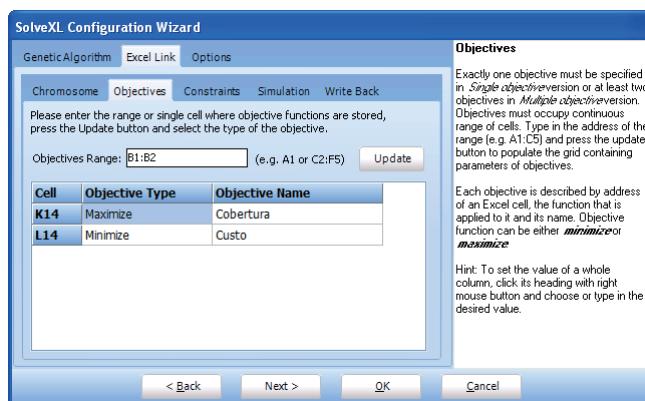

| 3.1.2 Componente SolveXL .....                                                                                              | 35        |

| 3.2 Estruturação do Algoritmo Genético .....                                                                                | 35        |

| 3.2.1 Codificação .....                                                                                                     | 36        |

| 3.2.2 Inicialização .....                                                                                                   | 38        |

| 3.2.3 Função Multi-Objetivo .....                                                                                           | 38        |

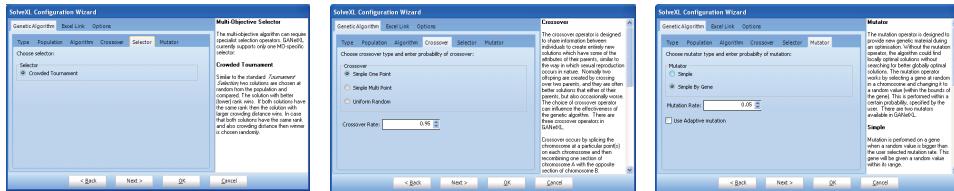

| 3.2.4 Operadores de seleção, cruzamento e mutação .....                                                                     | 47        |

| <b>RESULTADOS E DISCUSSÕES .....</b>                                                                                        | <b>49</b> |

| 4.1 Configuração do Algoritmo NSGA-II .....                                                                                 | 49        |

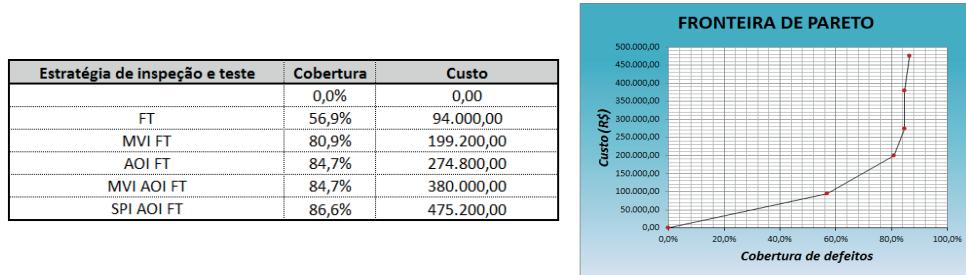

| 4.2 Estudo de caso 1: Geração da estratégia de inspeção e teste para uma placa eletrônica de baixa complexidade .....       | 50        |

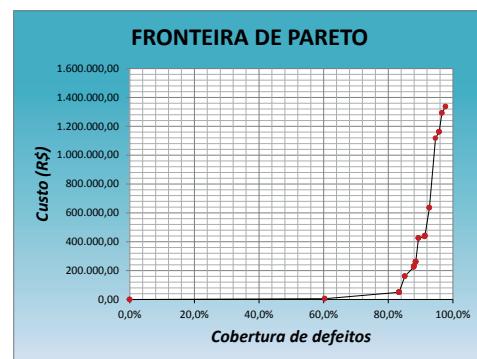

| 4.3 Estudo de caso 2: Geração da estratégia de inspeção e teste para uma placa eletrônica de média complexidade.....        | 52        |

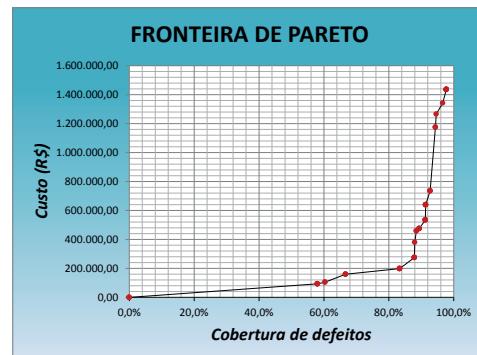

| 4.4 Estudo de caso 3: Geração da estratégia de inspeção e teste para uma placa eletrônica de alta complexidade.....         | 55        |

| 4.5 Considerações finais .....                                                                                              | 57        |

| <b>REFERÊNCIAS .....</b>                                                                                                    | <b>60</b> |

| <b>SOBRE O AUTOR .....</b>                                                                                                  | <b>64</b> |

# PLANEJAMENTO DAS INSPEÇÕES E TESTES NO PROCESSO DE MONTAGEM DE PLACAS ELETRÔNICAS

A produção de placas eletrônicas envolve um grande número de fatores relacionados a produto e processo que podem gerar defeitos, influenciando diretamente na qualidade final do produto. Entretanto, não existe uma técnica capaz de detectar todos os defeitos que podem ser gerados em uma placa eletrônica. Assim sendo, as diferentes técnicas existentes devem ser combinadas de forma adequada a fim de se atingir a maior cobertura de defeitos possível com o menor custo possível. Este capítulo visa explanar os diferentes tipos de defeitos que podem estar presentes durante a montagem das placas eletrônicas, as principais técnicas de inspeção e teste utilizadas para detectarem estes defeitos e por último discutir os aspectos mais relevantes para a definição da melhor estratégia de inspeção e teste para a montagem de uma placa eletrônica.

## 1.1 DEFEITOS NA MONTAGEM DE PLACAS ELETRÔNICAS

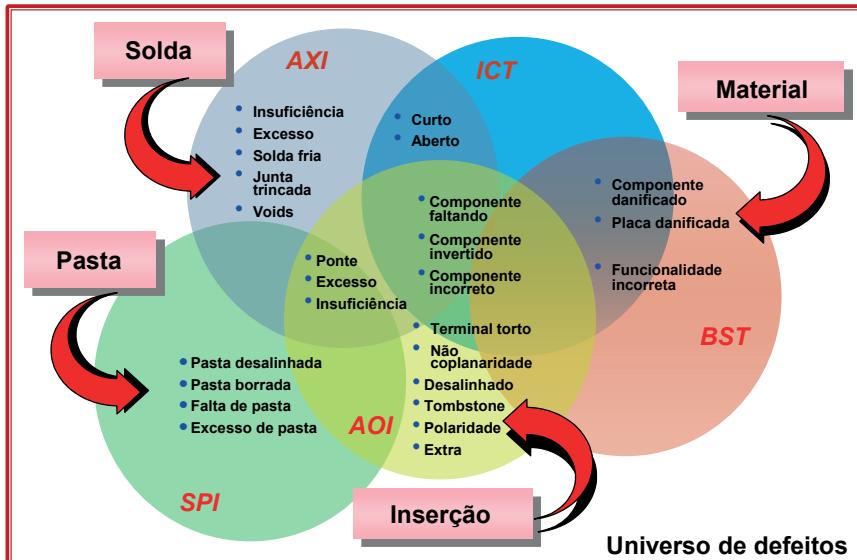

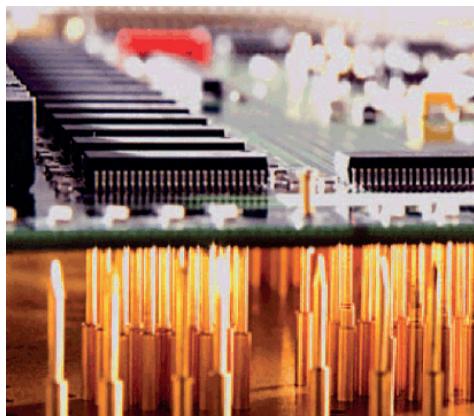

Existem atualmente dois tipos principais de tecnologia de montagem de placas eletrônicas: a tecnologia de montagem através de furos, conhecida pela sigla THT (*Through-Hole Technology*), e a tecnologia de montagem em superfície, denominado pela sigla SMT (*Surface Mount Technology*). As placas eletrônicas de tecnologia THT dominou o mercado até o final dos anos 80 vêm sendo substituída pela montagem SMT. Atualmente, menos de 15% do total de componentes produzido mundialmente são de tecnologia THT. Desta forma, este trabalho se restringirá seu estudo somente para placas eletrônicas de tecnologia SMT (Figura 2).

Figura 2 - Esquema de montagem de uma placa eletrônica de tecnologia SMT (DORO, 2004)

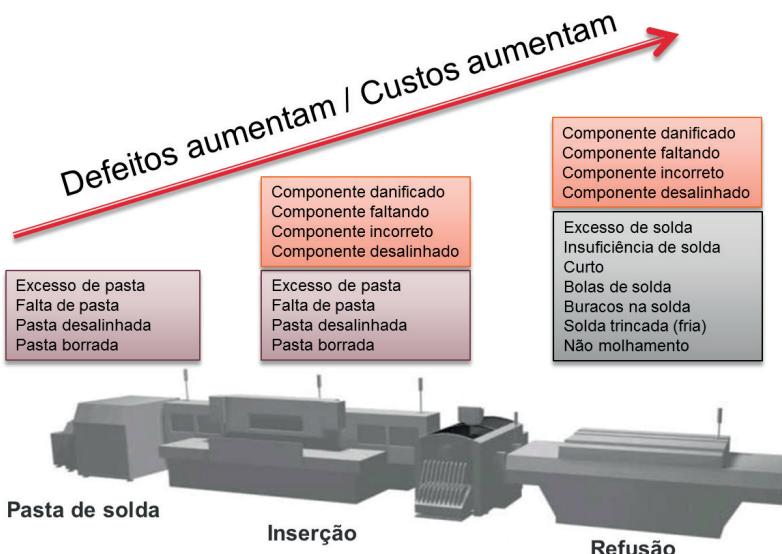

O processo de montagem SMT é um processo totalmente automatizado e consiste de três etapas principais. A primeira etapa consiste na deposição da pasta de solda<sup>1</sup> sobre a superfície da placa eletrônica, em seguida são inseridos os componentes eletrônicos nos locais onde foi aplicada a pasta de solda, e por fim, é realizada a soldagem por refusão<sup>2</sup>.

1 **Pasta de solda:** material constituído por um pó metálico que compõem a liga de solda e uma combinação de resina, ativadores, aditivos reológicos e solventes, chamado de fluxo de solda.

2 **Refusão:** ação de aplicar calor suficiente de modo que ocorra a separação da solda e do fluxo e posteriormente o derretimento da solda

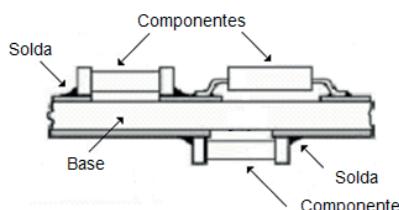

A deposição da pasta de solda é feita normalmente por um processo de impressão serigráfica. Neste processo um rodo pressiona e espalha a pasta de solda sobre uma tela metálica vazada, chamada de estêncil, permitindo a passagem da pasta somente sobre os locais desejados da placa eletrônica. Estima-se que cerca de 40 variáveis influem no resultado final do processo, tornando complexa a identificação da causa raiz que originou o defeito. Estudos mostram que 60% dos defeitos em montagem em placas eletrônicas podem ser atribuídos ao processo de impressão de pasta de solda. Deste modo, inspecionar a placa eletrônica imediatamente após a impressão de pasta de solda, além de evitar que defeitos sejam gerados nas próximas etapas de montagem, permite controlar o processo mais crítico. Os defeitos relacionados à aplicação da pasta de solda são: excesso ou falta de pasta de solda, pasta de soda desalinhada e pasta de solda borrada. A Figura 3 ilustra os aspectos que devem ser controlados durante a aplicação de pasta de solda para não ocasionarem defeitos nas próximas etapas do processo.

Figura 3 - Aspectos na aplicação de pasta de solda causadores de defeitos (COOMBS, 2001)

Por sua vez, a inserção de componentes sobre a pasta de solda aplicada é executada através de máquinas de inserção automática. Existem diferentes topologias de máquinas de inserção de componentes SMT, a maior diferença entre estas máquinas está no transporte do componente do alimentador para a placa eletrônica, sendo que a maioria utilizam bocais a vácuo para executar este transporte. Diferentes tipos de bocais são projetados para os variados tipos de componentes.

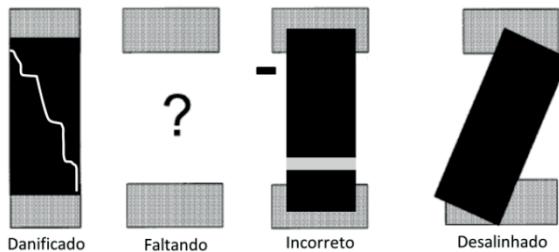

A exatidão e a repetibilidade das máquinas insensoras de componentes SMT é o resultado de uma série de parâmetros, entre eles sobressaem-se: exatidão do eixo de movimentação, resolução das câmeras de visão, algoritmos de visão, fixação da placa, programa de coordenadas, pressão de inserção dos componentes, tipos de bocais e alimentadores. A configuração e o controle inadequado destes parâmetros pode gerar uma série de defeitos, os quais são acentuados caso exista uma aplicação incorreta de pasta de solda sobre a placa eletrônica. Dentre os defeitos encontrados após processo de inserção destacam-se: componente danificado, componente faltando, componente inserido na posição incorreta (invertida, valor ou tipo incorreto e extra) e componente deslocado (Figura 5).

Figura 4 - Principais defeitos gerados na inserção dos componentes (Adaptado de COOMBS, 2001)

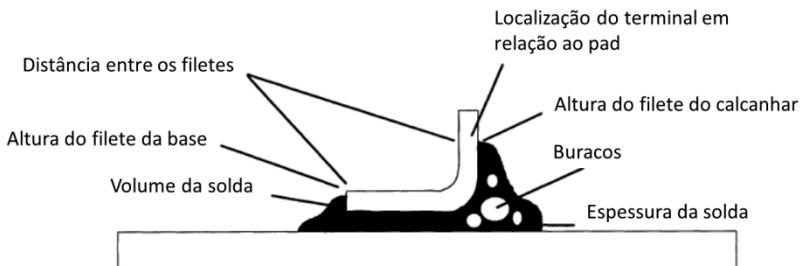

A refusão da pasta de solda é a última etapa a ser realizada, através deste processo é realizada a soldagem entre o componente e a placa. Esta etapa é realizada em um forno, denominado de forno de refusão. Este forno possui zonas com temperaturas diferenciadas ao longo do caminho percorrido pela placa eletrônica por uma esteira rolante. A refusão da pasta de solda acontece através do perfil térmico do forno, ou seja, a curva da temperatura da placa em função do tempo. Um perfil térmico mal ajustado para a placa eletrônica, bem como, uma incorreta aplicação de pasta de solda e inserção de componentes, geram uma série de defeitos, os quais se destacam: insuficiência ou excesso de solda, curto, buracos na solda, solda trincada (fria) e não molhamento. A Figura 5 apresenta as características que influenciam na confiabilidade da junta de solda gerando defeitos de montagem.

Figura 5 - Características que influenciam na confiabilidade da junta de solda (COOMBS, 2001)

Observa-se, portanto, que em cada etapa do processo de montagem de placas eletrônicas pode ser gerados uma série de defeitos. Destaca-se que estes defeitos são acumulativos e alguns são transformados em outros. Quanto mais tempo demorar em encontrar e corrigir estes defeitos mais custosos será os reparos (Figura 6).

Figura 6 - Processo de montagem de placas eletrônicas e principais defeitos encontrados em cada etapa do processo

Grande parte dos defeitos é controlada de forma atributiva, o que dificulta muito a inspeção e o controle do processo. Para prevenir ou corrigir esses defeitos requer-se um conhecimento apurado das relações de causa e efeito do processo de montagem. No entanto, um teste 100% do produto no final da linha sempre se torna necessária, pois um teste por amostragem pode causar erros do Tipo I e II. Há empresas que adotam a inspeção ou o teste 100% após cada etapa de processo para evitar o retrabalho e corrigir o processo o mais rápido possível. Entretanto, é fundamental conhecer e aplicar corretamente as técnicas de inspeção e teste no processo de montagem de placas eletrônicas.

## 1.2 TÉCNICAS DE INSPEÇÃO E TESTE NO PROCESSO DE MONTAGEM DE PLACAS ELETRÔNICAS.

As técnicas utilizadas em uma linha de montagem de placas eletrônicas para detectarem defeitos em uma placa eletrônica podem ser divididas em inspeção, testes estruturais e testes funcionais. A seguir serão apresentadas as particularidades destas técnicas.

### 1.2.1 Inspeção

A inspeção na linha de montagem de placas eletrônicas é realizada predominantemente através de métodos ópticos. Os principais defeitos detectados pela inspeção são defeitos de superfície, os quais podem ocorrer durante toda a etapa de montagem, como: riscos, coloração e manchas, componentes faltando, componentes incorretos e componentes

posicionados incorretamente; bem como, juntas abertas, curtos e varrições de espessura das juntas de solda.

Os equipamentos de inspeção podem ser posicionados na linha de montagem de placas eletrônicas, desde a inserção da placa nua na linha até a montagem final do produto. A seguir são apresentados os diferentes tipos de técnicas de inspeção usados para controlar o processo de montagem de placas eletrônicas.

#### *1.2.1.1 Inspeção visual manual (MVI)*

A inspeção visual manual consiste de um inspetor humano identificando os defeitos nas placas eletrônicas com o auxílio de uma lente de aumento ou até mesmo um sistema de câmera de vídeo. O ser humano é sem dúvida o mais flexível e inteligente de todos os sistemas de inspeção. Este possui habilidade de relembrar de vários detalhes dos critérios de inspeção, perceber detalhes de cor e geometria e interpretar novas e imprevistas circunstâncias, que são difíceis de serem alcançadas com qualquer tecnologia de software e hardware atualmente. Contudo, o elemento humano em um processo de inspeção contribui significativamente para a geração de erros de inspeção.

Os principais fatores na inspeção manual que levam os erros de inspeção são: velocidade de inspeção, fatiga do operador, julgamento do operador, resolução do equipamento, manipulação das partes, campo de visão e profundidade de campo. Os erros de inspeção podem ser minimizados a partir de um programa de treinamento e a utilização de critérios inspeção. A norma IPC-A-610E define padrões fotográficos de alvo, aceitável e defeitos de montagem de placas eletrônicas.

Contudo, como a produção de placas eletrônicas se caracteriza por ser um ambiente que demanda alta flexibilidade, onde montagens de lotes com diversos tamanhos devem ser suportadas com eficácia e agilidade. Tal fato requer uma excessiva atenção às atividades manuais e demais interações humanas envolvidas no processo. Busca-se neste modo, sempre que possível, a utilização das técnicas de inspeção automática a fim de suprir as deficiências encontradas na inspeção visual manual.

#### *1.2.1.2 Inspeção óptica automática (AOI)*

A inspeção óptica automática oferece vários benefícios em relação à inspeção humana. Através de uma alta ampliação óptica e com o uso da automação, as máquinas AOI fornecem resultados mais confiáveis e consistentes do que os operadores humanos, especialmente nos componentes menores e em placas densas. Adicionalmente, as máquinas AOI reduzem o número de inspetores humanos necessários e os custos associados e ainda aumenta o rendimento da produção.

As máquinas AOI são mais eficientes em detectar os defeitos relacionados à presença, orientação e localização de componentes, embora consiga detectar alguns

defeitos relacionados às juntas de solda. Estas máquinas normalmente trabalham em linha e é integrada a estação de reparo, podendo ser posicionadas em várias partes da linha de montagem.

Os sistemas de inspeção óptica automática utilizam câmeras de alta ampliação óptica, vertical e angular, em conjunto com um sistema de iluminação, esteiras, estágios de rápida movimentação XY e processadores para controlar o sistema. O processo começa com a captura da imagem através de uma ou mais câmeras. Em seguida, o processador irá transformá-la em uma matriz de elementos de imagem, ou pixels. Para cada pixel é atribuído uma valor analógico, dependendo da luminosidade. Este é então convertido num valor digital para mais adiante ser analisado ou gravado. A maioria das máquinas AOI pode ser programada pelo pessoal de nível técnico. Dependendo da técnica de programação, das ferramentas de software disponibilizadas e do sistema operacional, o tempo de programação pode variar enormemente entre as máquinas.

As primeiras máquinas AOI utilizavam apenas uma imagem de referência, chamada de “*Golden-board*”, correlacionando essa imagem de referência com as imagens recém-adquiridas. Esta técnica conseguia prover de uma rápida programação, porém o diagnóstico de defeitos não era tão específico, não sendo possível definir a posição exata dos componentes e os ângulos de rotação, as tolerâncias numéricas específicas para os componentes e o formato das juntas de solda.

Atualmente as máquinas AOI usam os dados originais dos softwares de desenvolvimento da placa eletrônica, assim conseguem quantificar a rotação e a translação do componente e o formato da junta de solda. Neste caso, o tempo de programação pode não ser muito rápido, caso não exista uma biblioteca abrangente contendo os modelos de componentes que serão soldados na placa.

#### *1.2.1.3 Inspeção Raio-X automática (AXI)*

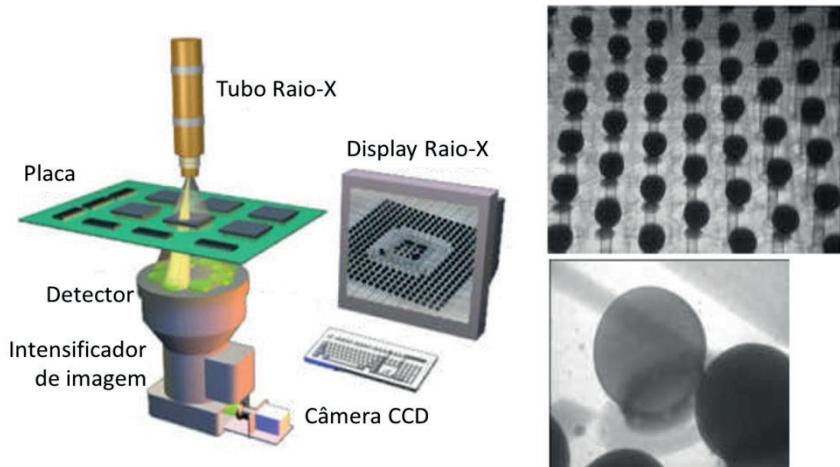

A inspeção óptica automática é eficiente na inspeção de placas eletrônicas que possuem as juntas de solda visíveis. No entanto, muitas placas eletrônicas atualmente estão usando tecnologias de circuitos integrados com as juntas de solda não são visíveis, tal como o BGA. Neste caso, é necessário utilizar outras tecnologias de inspeção. As máquinas de inspeção Raio-X automática, também chamadas de máquinas AXI, é um equipamento que pode não apenas verificar as juntas de solda em baixo dos componentes eletrônicos, mas também revelar muitos defeitos em juntas de solda que podem não ser visíveis com equipamentos de inspeção de óptica comum.

Deste modo, a máquina AXI é eficaz especialmente nos defeitos relacionados à confiabilidade das juntas de solda, ocultas ou visíveis, incluindo juntas de solda em aberto ou em curto e buracos na solda. Elas normalmente são inseridas na linha de montagem após o forno de refusão para monitorar os defeitos após as placas eletrônicas passarem pelo processo de soldagem.

As máquinas AXI exibem imagens em escala de cinza, que representam variações na forma e espessura de um objeto. Geometrias de alta densidade produzem uma imagem mais escura do que aquelas com menor densidade ou espessura. Portanto, é possível quantitativamente medir estas geometrias e desenvolver correlação entre aceitável ou inaceitável. Durante a inspeção, os raios-x emitidos a partir da fonte, passam através da placa eletrônica para um intensificador de imagem. Em seguida, as imagens são dirigidas, a partir do detector por meio de espelhos, para uma câmera de vídeo, onde as imagens digitalizadas são enviadas para um processador de imagem para aprimoramento, exibição e análise (Figura 7).

Figura 7 - Princípio de funcionamento de uma máquina de inspeção a raio-x (NICOLET, 2013)

Com base nos dados da imagem resultante, um algoritmo de computador pode determinar a forma exata do filete da junta de solda e detecção de vazios dentro da junta. É possível também calcular o volume de solda. Essas medidas indicam a qualidade da solda. A técnica pode também detectar pontes de solda que pode resultar em curtos-circuitos.

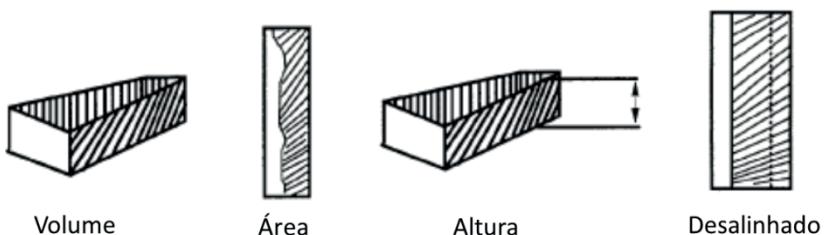

#### 1.2.1.4 Inspeção de pasta de solda (SPI)

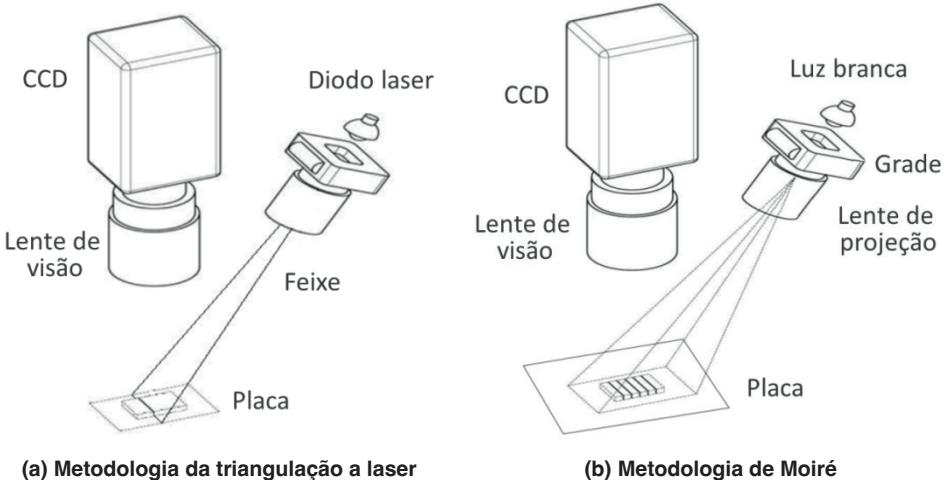

As máquinas de inspeção de pasta de solda, também conhecidas como SPI (*Solder Paste Inspection*), são sistemas de inspeção utilizados para inspecionar a placa após a inserção de pasta de solda. Os defeitos que podem ser detectados por uma máquina SPI relacionam-se ao volume, área e posicionamento da pasta de solda impressa sobre a placa eletrônica. Atualmente, duas técnicas principais de inspeção de pasta de solda são utilizadas pelas máquinas SPI, uma através da metodologia da triangulação a laser e outra baseada na metodologia de Moiré (Figura 8).

Figura 8 - Técnicas de inspeção de pasta de solda (PEALLAT, 2013)

A tecnologia de triangulação a laser normalmente é combinada com uma imagem 2D. A altura da pasta de solda é dada pelo desvio do traço do laser e o formato da pasta de solda por sua vez é determinado pela imagem 2D. O método de levantamento por triangulação a laser pode detectar apenas a altura de um ponto sobre o depósito de solda, sendo incapaz de refletir a verdadeira altura da pasta de solda depositada sobre a placa. A topografia Moiré é um método de medição tridimensional por modulação de fase. Neste método particular as linhas são projetadas no objeto e moduladas por interferência de franjas e pelo movimento grades. Através deste método é possível de ser medida a altura e volume da pasta de solda.

### 1.2.2 Testes estruturais

Na montagem de placas eletrônicas, os testes diferem da inspeção primeiramente pelo fato de utilizarem métodos elétricos no lugar de métodos ópticos. Outra grande diferença é que os testes são utilizados após o processo de soldagem ser concluído. Os testes estruturais focam no teste da estrutura física da placa, ou seja, na integridade das juntas e componentes. Os testes estruturais podem verificar a existência de circuitos abertos e curtos-circuitos, medir componentes individuais, detectar a presença e orientação de componentes e ainda fazer alguns testes funcionais mais simples.

Os testes elétricos tradicionais usam pontas de provas elétricas para verificar se a placa eletrônica foi montada corretamente. Estes testes podem ser realizados por um dispositivo formado por múltiplas pontas de provas, no qual os engenheiros de teste adotaram o termo “cama-de-pregos”. Neste dispositivo, cada ponta de prova é posicionada de modo que possa entrar em contato simultaneamente com os pontos de testes da placa

eletrônica (Figura 9a). Outra forma alternativa deste teste é através de um equipamento denominado *flying probe*, no qual utiliza pontas de provas flutuantes. Neste caso, o processo de teste é executado por pontas de provas que se deslocam em alta velocidade através da placa eletrônica fazendo o contato com os pontos de teste da placa eletrônica de forma sequencial (Figura 9b).

(a) Teste por “cama de pregos”

(b) Teste por *flying probe*

Figura 9 - Testes estruturais utilizando pontas de provas elétricas (PRESTOY, 2010)

Outro conceito utilizado para execução dos testes estruturais é pelo método chamado *Boundary Scan - JTAG*. Este método define um padrão de conexão entre o sistema de teste e a placa eletrônica na qual permite testar os componentes da placa eletrônica que possuem o padrão JTAG, utilizando para isto um módulo de teste e um software dedicado. A seguir são apresentados os diferentes tipos de testes estruturais.

#### 1.2.2.1 Teste MDA (*Manufacturing Defects Analyzer*)

O teste MDA visa identificar os defeitos de montagem da placa eletrônica de uma maneira mais rápida e acessível em custo se comparado com o teste ICT. Os principais defeitos detectados pelo teste MDA são curtos, circuito abertos e defeitos em componentes analógicos passivos.

Esta metodologia de teste usa um dispositivo elétrico de cama-de-pregos ou *flying-prober* para acessar os pontos de testes da placa eletrônica e medir os sinais elétricos. Usando fonte de sinais programável e sensoriais, os componentes são isolados uns dos outros para permitir que eles sejam testados no circuito. Usando um padrão complexo de medições impedância, os testes MDA podem realizar ainda um teste global sem a aplicação de energia na placa eletrônica.

Os dados provenientes do software de desenvolvimento da placa eletrônica podem ser usados para criar um programa de teste para o equipamento MDA, as informações do diagrama elétrico (*netlist*), tipo, posição e valor dos componentes são suficientes para automaticamente gerar o programa de teste. No entanto, geralmente o programa de teste gerado automaticamente pelo software dos equipamentos MDA requer um refinamento e otimização.

#### 1.2.2.2 Teste In-Circuit (ICT)

O teste ICT possui a mesma metodologia do teste MDA, diferindo apenas pelo fato deste executar os testes com a placa eletrônica alimentada por uma fonte de tensão. Desta forma, este tipo teste consegue uma maior cobertura de defeitos. O teste ICT pode verificar a existência de circuitos abertos e curto-circuitos, medir resistores e indutores individuais e detectar a presença e orientação de diodos, transistores e circuitos integrados. Também podem ser testadas lógicas digitais através da introdução de uma série de vetores de testes e pela verificação de saída. O teste ICT normalmente não pode determinar a polaridade de capacitores polarizados ou identificar a falta de capacitores de *by-pass*. No entanto, ele pode detectar capacitores em curto-circuito e indutores em aberto.

Atualmente, com a produção de placas eletrônicas complexas e densas, possivelmente com multi-camadas e com circuitos integrados do tipo BGA, os testes MDA e ICT torna-se ineficiente, pois o acesso aos pontos de testes é limitado. Uma vez que existem tamanhos mínimos e regras de espaçamento mínimas para inserir pontos de testes na placa eletrônica. Além disso, os pontos de teste podem introduzir interferência eléctrica indesejada, especialmente em sistemas de alta frequência.

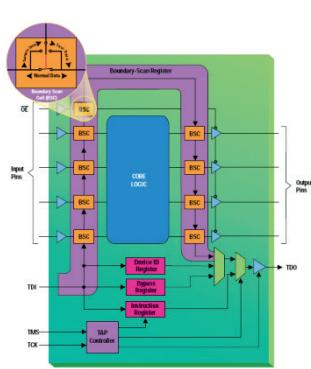

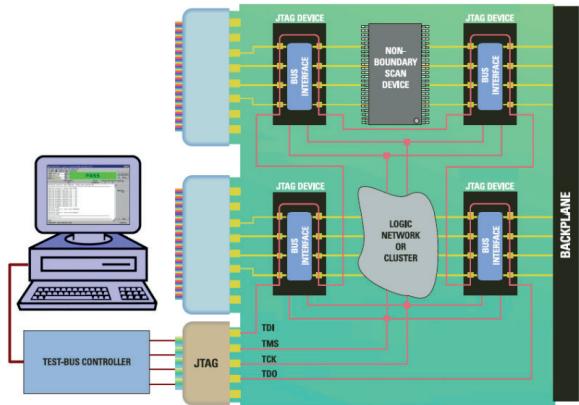

#### 1.2.2.3 Teste Boundary Scan-JTAG (BST)

O *Boundary Scan* é uma técnica que permite controlar e observar os pinos dos circuitos integrados que possuem o padrão JTAG/IEEE 1149.1 (Figura 10a). O padrão *Boundary Scan*-JTAG fornece meios de testar conexões nos circuitos integrados em uma placa eletrônica montada sem usar pontas de prova físicas de teste, usando para isto uma porta de acesso ao teste. Dentre as vantagens do uso desta técnica destacam-se: execução de testes de conexão em encapsulamentos de componentes sem terminais aparente (BGA), plataforma de teste flexível e dispensa o uso de “cama de pregos”.

A arquitetura de teste proposta neste padrão consiste em uma porta de acesso (TAP - *Test Access Port*) e uma lógica de controle, que inclui a decodificação de instruções de teste e um conjunto de registradores, dentre os quais o registrador de deslocamento de periferia composto por células de memorização e varredura, conhecidas como células *Boundary Scan*. Cada uma destas células pode capturar dados em suas entradas, atualizar os dados sobre as saídas, passar dados à célula vizinha e ser transparente ao sistema.

(a) Arquitetura de um circuito integrado com padrão JTAG

(b) Estrutura necessária para o teste Boundary Scan

Figura 10 - Particularidades teste Boundary Scan-JTAG (adaptado de TEXAS INSTRUMENT, 1998)

Para que o teste *Boundary Scan-JTAG* ocorra é necessário que projeto da placa eletrônica seja adequado e que possua circuitos integrados que suportem esta tecnologia, e ainda, um controlador do barramento de teste e um software para configuração e execução do teste. (Figura 10b). O padrão de teste consiste em conectar componente em seu componente vizinho através dos pinos TDI (*Test Data In*) e TDO (*Test Data Out*), formando um caminho serial. Em função deste caminho ser serial, existe um sinal de sincronismo dedicado nas células *Boundary Scan* através do pino TCK (*Test Clock*). Um circuito adicional dedicado ao controle de teste pode ser ativado pelo pino TMS (*Test Mode Select*).

Através da tecnologia *Boundary Scan* é possível testar a conexão das trilhas ligadas aos circuitos integrados com padrão JTAG e realizar testes funcionais de componentes ou partes do circuito que estejam ligados a estes circuitos integrados. Podem ser realizados testes funcionais de natureza digital, como por exemplo: emular os protocolos, controlar e testar memórias, chaves, etc. Para a realização de testes funcionais analógicos faz-se necessário introduzir conversores A/D e D/A no circuito.

### 1.2.3 Testes funcionais (FT)

Os testes funcionais são usados para verificar a confiabilidade funcional da placa. Empregado sempre no final da linha, um teste funcional simula o ambiente operacional de um produto para verificar se o mesmo está operando corretamente. Os testes funcionais são os únicos testes que podem detectar um defeito em nível de sistema. No entanto, normalmente os testes funcionais não indicam o defeito de forma pontual, necessitando executar um diagnóstico posterior por um especialista para que se possa descobrir a causa do defeito.

Tipicamente a interface entre o teste funcional e a placa é feita através de conectores ou pontos de testes, onde é simulado o ambiente elétrico final em que a placa será usada. A placa eletrônica é alimentada e submetida a uma sequência de sinais. As respostas são monitoradas em pontos específicos para garantir a funcionalidade está correta.

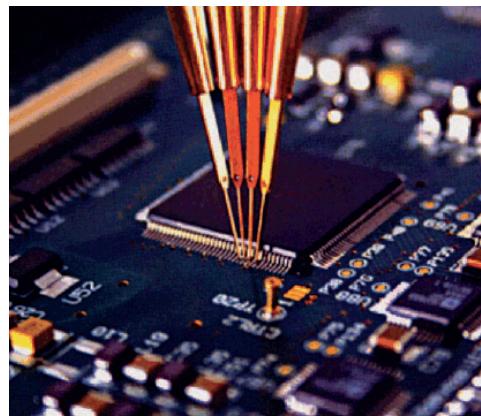

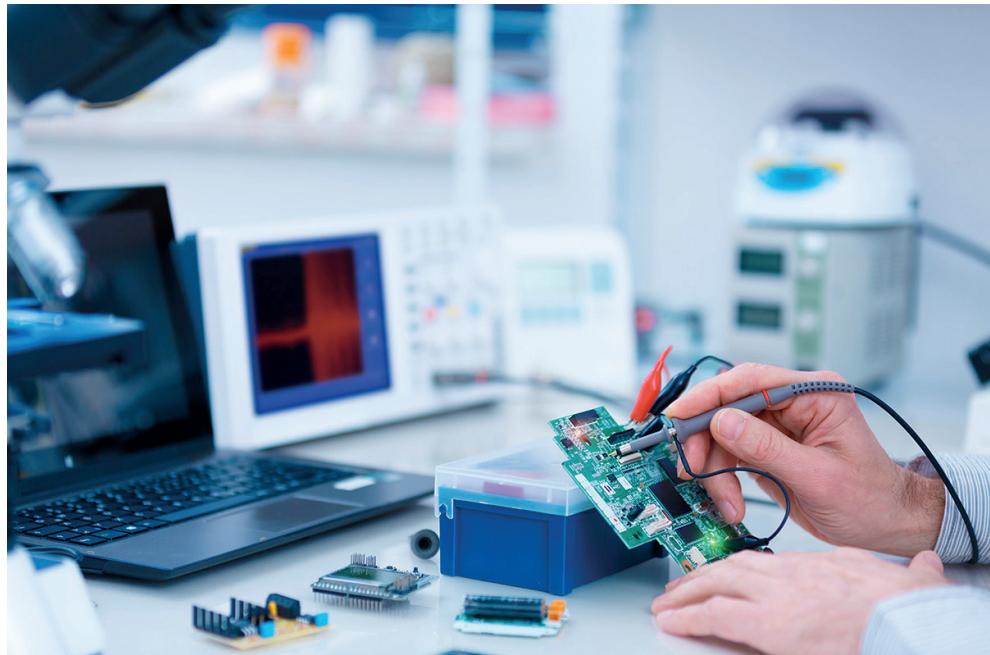

A forma mais comum de teste funcional, conhecido como *hot mock-up*, simplesmente verifica se a placa eletrônica está funcionando corretamente. Os testes funcionais mais sofisticados envolvem a placa em uma gama completa de testes operacionais. Neste segundo caso, existe um software de teste no qual permite que os operadores da linha de produção possam realizar o teste funcional de forma automática através de um computador (Figura 11). Para isso, o software se comunica com instrumentos externos programáveis como multímetros digitais, placas de I/O, portas de comunicação, entre outros.

Figura 11 - Teste funcional de placa eletrônica (PETERSON, 2020)

Geralmente os testes funcionais não são flexíveis, sendo dedicados para cada modelo de placa. Em alguns casos, se os defeitos de montagem não forem anteriormente removidos, o teste funcional pode danificar o circuito. Porém, a principal dificuldade de implantar um teste funcional está na complexidade placa. Por fim, destaca-se que o teste funcional é mais eficiente na detecção de componentes danificados, falhas funcionais e falhas paramétricas.

### 1.3 ESTRATÉGIA DE INSPEÇÃO E TESTE

A cobertura de defeitos pode ser definida como “a razão de defeitos detectáveis pelo número total de defeitos”. Uma vez que não existe uma única técnica de inspeção e teste capaz de obter uma cobertura de 100% de todos os defeitos, torna-se necessário combinar racionalmente diferentes técnicas para garantir a qualidade da placa.

Cada uma das técnicas de inspeção e teste apresentadas possui características únicas de custo-benefício. A Tabela 1 apresenta uma qualificação das diferentes técnicas de inspeção e teste, baseada na sua capacidade de discernir defeitos. Cabe destacar que a qualificação poderá variar ligeiramente, dependendo das diferentes tecnologias, equipamentos e procedimentos usados.

Tabela 1 - Cobertura de defeitos das principais técnicas de inspeção e teste (VERMA, 2002)

|                                    | MVI | SPI | AOI | AXI | MDA | ICT | BST | FT |

|------------------------------------|-----|-----|-----|-----|-----|-----|-----|----|

| Curto                              | ◆   | ◆   | ◆   | ✓   | ◆   | ◆   | ◆   | ◆  |

| Ausência de solda                  | ✗   | ◆   | ◆   | ✓   | ◆   | ◆   | ◆   | ◆  |

| Confiabilidade da solda            | ✗   | ◆   | ◆   | ✓   | ✗   | ✗   | ✗   | ✗  |

| Componente incorreto               | ✗   | ✗   | ✓   | ✗   | ✓   | ✓   | ◆   | ◆  |

| Componente faltando                | ◆   | ✗   | ✓   | ✓   | ✓   | ✓   | ◆   | ◆  |

| Componente danificado              | ✗   | ✗   | ✗   | ✗   | ◆   | ◆   | ◆   | ✓  |

| Orientação incorreta do componente | ◆   | ✗   | ✓   | ◆   | ✓   | ✓   | ◆   | ◆  |

| Confiabilidade funcional           | ✗   | ✗   | ✗   | ✗   | ✗   | ✗   | ◆   | ✓  |

|                                                                                              |                                                                                                           |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| <b>Legenda:</b><br><br>✗ Baixa ou nenhuma cobertura<br>◆ Média cobertura<br>✓ Alta cobertura | <b>Suposições:</b><br>5000 nós, 25000 juntas de soldas, 80% de acesso pelo ICT e MDA, 10 componentes BGAs |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

A estratégia de inspeção e teste consiste em definir as técnicas que serão utilizadas para verificar a confiabilidade e funcionalidade do produto eletrônico produzido. Esta deve ser desenvolvida apresentando um balanço correto entre o investimento financeiro e o desempenho da inspeção e do teste em identificar os defeitos gerados no produto.

Até os anos 90, a melhor estratégia de inspeção e teste consistia em executar uma inspeção visual manual durante a montagem e em seguida, fazer o teste ICT e funcional no produto. Com isto, era possível detectar 100% dos defeitos em quase todas as placas eletrônicas produzidas. Atualmente, esta estratégia nem sempre é eficaz. As placas possuem um número significativamente maior de componentes e juntas de solda do que há alguns anos atrás. Um número maior de componentes normalmente significa um custo maior para cada placa eletrônica, resultando em maiores custos de WIP (estoque intermediário) e de refugos. Uma vez que o aumento da complexidade da placa eletrônica resulta normalmente em rendimentos mais baixos e maiores dificuldades no diagnóstico quando os defeitos ocorrem. Além disso, com a redução constante nas dimensões dos componentes, aumentam o desafio de soldá-los corretamente na placa eletrônica. Componentes como 01005 e *Ultra fine-pitch* são exemplos desta mesma categoria. Ao mesmo tempo, o acesso de 100% dos pontos de teste elétrico, no qual permitia o sucesso do teste ICT, ultimamente é muito difícil de ocorrer. O acesso visual das juntas de solda também está sendo reduzido, tal como as juntas dos componentes BGA. Ainda pode-se destacar que as pressões de mercado, o curto tempo para projetar o produto e configurar o processo e a redução dos recursos de manufatura a fim de reduzir custos, estão colocando os fabricantes de produtos eletrônicos em uma situação cada vez mais complicada.

Assim, para uma empresa se manter competitiva é necessário elaborar uma estratégia de inspeção e teste que aborda todas essas tendências. Os principais fatores que devem ser levados em consideração na elaboração de uma estratégia de inspeção e teste são:

- Projeto da placa eletrônica: características como: encapsulamentos de componentes, pontos de acesso, componentes *boundary-scan*, juntas ocultas (BGA), entre outros, influenciam muito na ocorrência de defeitos e na eficiência da técnica de inspeção ou teste e devem ser considerado.

- Espectro de defeitos: entender os diferentes tipos de defeitos, indicadores de processo e defeitos potenciais; possuir dados precisos sobre os níveis de defeitos e espectro defeito; ter conhecimento onde os defeitos são introduzidos no processo e onde eles podem ser detectados são fundamentais para a escolha da técnica de inspeção e teste.

- Cobertura de defeitos: a cobertura de defeitos da inspeção e do teste deve ser compatível com os principais defeitos que ocorrem na manufatura das placas eletrônicas. É importante possuir uma visão holística da estratégia de teste, tanto a partir de um ponto de vista de melhoria do processo, bem como a um ponto de vista de contenção defeito. Destaca-se que para uma ideal contenção de defeito, o sistema de inspeção e teste deve ser colocado logo após cada etapa de montagem.

- Rendimento: o rendimento da inspeção e do teste deve ser capaz de suprir o volume de produção da linha.

- Custo: para uma estratégia de teste econômica, deve ser considerado o custo de aquisição do equipamento, programação, operação e manutenção compatíveis com o retorno do investimento. Ressalta-se que quanto mais cedo for a captura defeitos no ciclo de vida do produto e no processo de fabricação menor será os custos da não qualidade.

Conclui-se que a formulação da estratégia de inspeção e teste eficaz depende de vários fatores, dentre os quais se sobressai às características do produto em questão. Como cada técnica de inspeção e teste possui níveis diferentes desempenho, a definição da melhor estratégia de inspeção e teste torna-se um problema com muitas dimensões de complexidade. Neste caso, uma abordagem moderna de análise deve ser adotada. Sem uma abordagem de análise quantitativa eficaz, não existir um número elevado de escolhas, e ainda, as características de sobreposição das diferentes técnicas de inspeção e teste tornarão processo de optimização da estratégia difícil e demorado, e provavelmente levarão a resultados questionáveis na melhor das hipóteses.

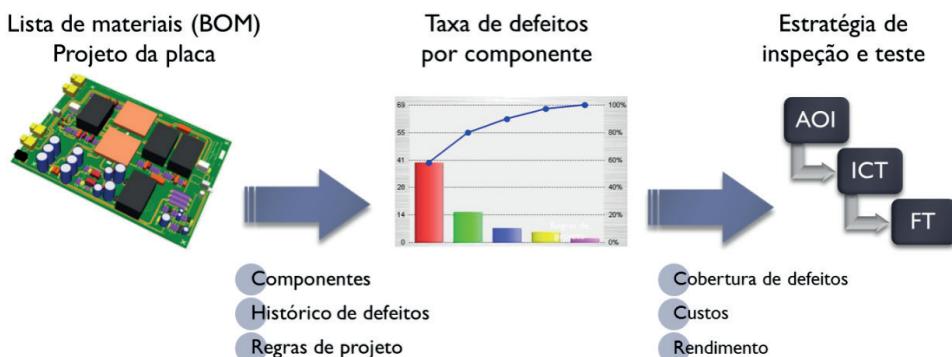

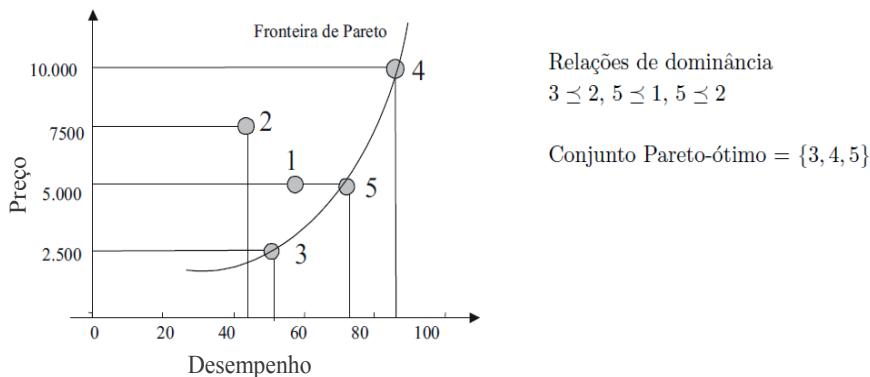

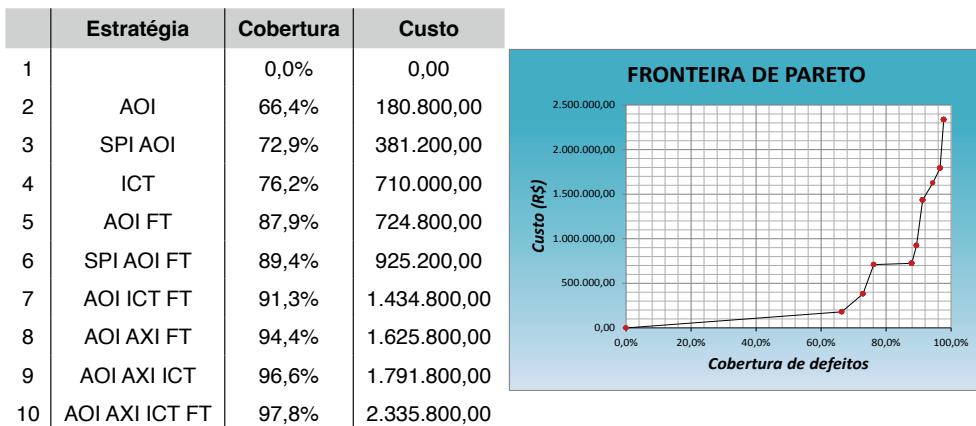

Neste trabalho a abordagem adotada para o desenvolvimento da estratégia de inspeção e teste será baseada na sugerida por Verma et al., 2000. Nesta abordagem, constrói-se um diagrama Pareto de defeito utilizando um modelo de previsão de defeitos. A partir destas informações, determinam-se as técnicas de inspeção e teste mais eficazes para capturar estes defeitos usando uma ferramenta de modelagem/simulação que contém a cobertura de defeito de cada técnica de inspeção e teste. Existem outros fatores podem ser incluídos neste modelo como: custo (programação, operação, investimento) e rendimento (tempo de depuração, análise e programação). A Figura 12 apresenta uma ilustração simplificada do modelo de desenvolvimento da estratégia de inspeção e teste adotado como base para este trabalho, no qual são mostrados os principais passos e as entradas e saídas.

Figura 12 - Modelo de desenvolvimento da estratégia de inspeção e teste (Adaptado de VERMA et al., 2000)

A entrada principal para este modelo é o projeto da placa eletrônica, ou seja, a lista de materiais (BOM) e o projeto da placa. Os componentes da placa eletrônica são então classificados em categorias elétricas e físicas. Baseado em dados históricos, a qualidade dos componentes de entrada (defeitos elétricos) pode ser aproximado com a classificação elétrica; de forma semelhante, as taxas de defeitos de montagem (defeitos físicos) podem ser estimadas com a classificação física. A saída das classificações combinadas, elétricas e físicas, é o espectro de erro estimado e os níveis de defeitos com base na BOM. Em seguida, é analisado a violações de regras de projeto. Quando uma regra de projeto (DFM) é violada, o impacto do defeito da violação é considerado. Após essa análise, uma boa aproximação do espectro da taxa de defeito da placa eletrônica está disponível.

Com esta informação, o impacto do uso de diferentes estratégias de inspeção e teste pode ser modelado. Por exemplo, estimativas podem ser feitas do impacto do uso de apenas a inspeção MVI e teste funcional, ou inserido uma inspeção AOI com o teste ICT e funcional, ou ainda, uma inspeção AXI com o teste ICT e funcional. Com base nestas análises, a estratégia de inspeção e teste ideal pode ser determinada para uma placa eletrônica em particular. O modelo sugere ainda fornecer o rendimento e os custos de reparo e refugo estimados.

### **1.3.1 Padrões de avaliação a cobertura de defeitos**

A avaliação da eficiência da estratégia de inspeção e teste pode ser feita principalmente pela cobertura de defeitos atingida. Recentemente vários padrões têm sido propostos para avaliar a cobertura de defeitos de uma estratégia de inspeção e teste, entre eles destacam-se: MPS, PPVS e PCOLA/SOQ. Estes modelos são comparáveis e diferem apenas em seu nível de abstração. Os mesmos descrevem como o universo de defeitos de uma placa eletrônica pode ser categorizado. O PCOLA/SOQ é o mais detalhado dos modelos, o qual apresenta oito grupos de defeitos. A Tabela 2 apresenta a discriminação dos defeitos contemplados por cada modelo.

Tabela 2 - Categorias de defeitos versus tipos de modelos (LOTZ et al., 2006)

|           |                      |                                      |

|-----------|----------------------|--------------------------------------|

| MPS       | PPVS                 | PCOLA/SOQ                            |

| Material  | Value                | Correct<br>Live                      |

| Placement | Presence<br>Polarity | Presence<br>Alignment<br>Orientation |

| Solder    | Solder               | Short<br>Open<br>Quality             |

Nota-se que o nível de representação de defeitos do modelo MPS é dividido dentro de uma hierarquia em outros níveis nos modelos PPVS e PCOLA/SOQ. É importante entender como os defeitos definidos no universo de defeitos correlacionam-se individualmente em cada modelo. Por exemplo, o defeito “Componente desalinhando” para o modelo MPS corresponde a categoria *Placement*, já para o modelo PPVS a categoria *Presence* enquanto que para o modelo PCOLA/SOQ para a categoria *Alignment*.

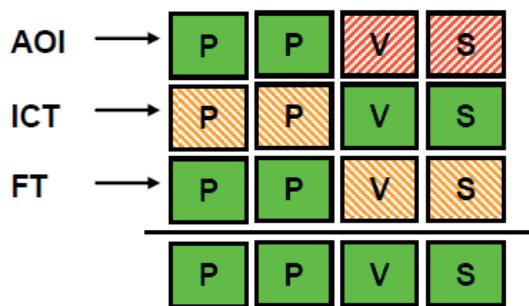

Todos estes modelos provem de um equivalente padrão para determinar a cobertura atingida pela estratégia de inspeção e teste. A Figura 13 mostra um exemplo de qualitativo de como o modelo PPVS analisa a cobertura de defeitos de uma estratégia de inspeção e teste que combina as seguintes técnicas AOI, ICT e FT.

Figura 13 - Cobertura de defeitos avaliados pelo modelo PPVS (LOTZ et al., 2006)

Nota-se que neste exemplo o modelo PPVS avalia a estratégia de inspeção e teste é capaz de capturar todos os defeitos. Na prática os modelos avaliam as técnicas de inspeção e teste para cada tipo de componente existente na placa eletrônica, gerando um índice para categoria de defeito por componente e um índice geral da estratégia de inspeção e teste.

# ALGORITMOS GENÉTICOS COMO FERRAMENTA PARA O PLANEJAMENTO DA ESTRATÉGIA DE INSPEÇÃO E TESTE

A solução para um problema de planejamento automático clássico, no qual se enquadra o escopo deste o trabalho, é encontrar uma sequência de ações que, ao serem executadas em determinada ordem, permite transitar de um estado inicial para um objetivo. O programa que permite resolver essa classe de problemas é dito planejador.

Conforme mencionado no capítulo 1, existem inúmeros planejadores apresentados pela comunidade científica, bem como inúmeros métodos sob os quais os planejadores são implementados com o intuito de obter resultados cada vez mais satisfatórios. Dentre estes métodos destacam-se os Algoritmos Genéticos, no quais vários trabalhos abordando este tema foram executados apresentando sua eficácia.

Algoritmos Genéticos (AG) são algoritmos de busca baseados nos mecanismos de evolução natural e na genética. Criados inicialmente por John Holland em seu trabalho intitulado de *“Adaptation in Natural and Artificial Systems”* em 1975, os AG é parte da Computação Evolucionária, que é uma área em crescimento da IA.

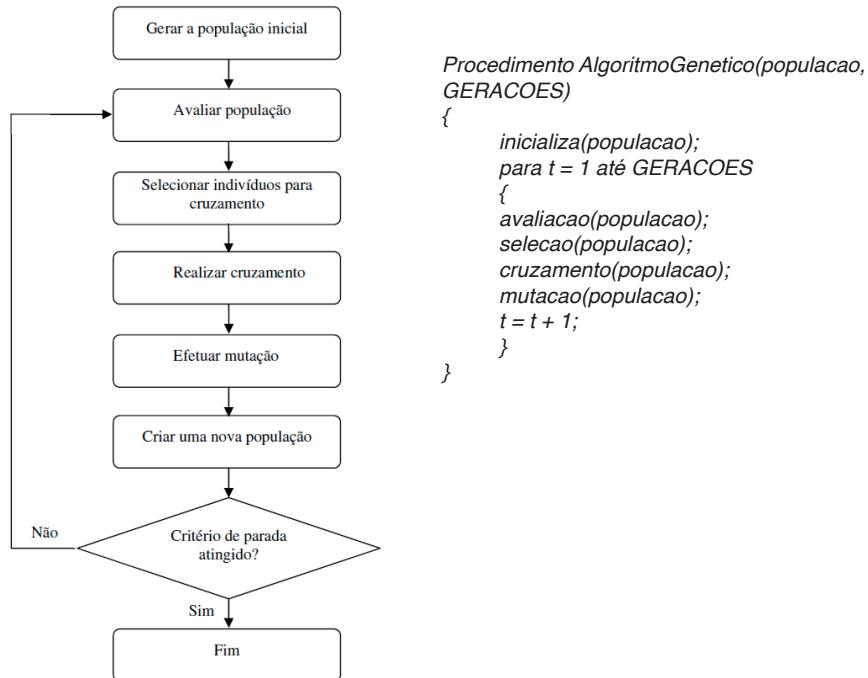

O conceito básico consiste que os indivíduos mais aptos sobrevivem e geram descendentes com suas características hereditárias. Desta forma, uma população de possíveis soluções para o problema considerado evolui de acordo com operadores probabilísticos concebidos de forma similar à teoria biológica (cruzamento genético, mutações, sobrevivência dos mais aptos), de modo que há uma tendência de que os indivíduos mais aptos representem soluções cada vez melhores à medida que o processo evolutivo continua. A forma geral e simplificada de um AG é apresentada na Figura 14.

Figura 14 - Fluxograma e código principal básico do Algoritmo Genético

Basicamente, o que um AG faz é criar uma população de possíveis respostas para o problema a ser tratado para depois submetê-la ao processo de evolução, desta forma o AG é constituído pelas seguintes etapas:

- Inicialização: inicia-se com uma população aleatória de indivíduos, também chamados de cromossomos (candidatos à solução do problema);

- Avaliação: avalia-se a aptidão de cada indivíduo (função objetivo ou *fitness*) onde é feita uma análise para que se estabeleçam quão bem eles respondem ao problema proposto;

- Seleção: os indivíduos são selecionados para a reprodução, os métodos de seleção podem ser determinísticos ou probabilísticos;

- Cruzamento: características das soluções escolhidas são recombinadas, gerando novos indivíduos;

- Mutação: características dos indivíduos resultantes do processo de reprodução são alteradas, acrescentando assim variedade à população;

- Finalização: verifica se as condições de encerramento da evolução foram atingidas, retornando para a etapa de avaliação em caso negativo e encerrando a execução em caso positivo.

Portanto, os AG trabalham com uma população de soluções iniciais, chamadas cromossomos, que através de diversas operações vão sendo evoluídas até que se chegue a uma solução que melhor atenda a algum critério específico de avaliação. Para que isto ocorra, a cada geração os cromossomos são avaliados segundo uma função que mede o seu nível de aptidão, chamada também de função de *fitness*. Os cromossomos que tiverem o melhor *fitness* são selecionados para darem origem à próxima geração, através de operadores de busca como cruzamentos e mutações.

Os AG são particularmente aplicados em problemas complexos de otimização; problemas com diversos parâmetros ou características que precisam ser combinadas em busca da melhor solução; problemas com muitas restrições ou condições que não podem ser representadas matematicamente e problemas com grandes espaços de busca.

Dentre suas principais vantagens dos AG, destacam-se:

- São fáceis de serem implementados em computadores;

- Adaptam-se bem a computadores paralelos;

- São facilmente hibridizados com outras técnicas;

- Funcionam com parâmetros contínuos ou discretos;

- Não afetada por descontinuidades na função ou em suas derivadas;

- São bons para atacar problemas com espaços de busca intratavelmente grandes, que não podem ser resolvidos por técnicas tradicionais.

Nos itens a seguir serão descritos com mais detalhes cada uma das etapas do AG.

## 2.1 INICIALIZAÇÃO (CODIFICAÇÃO)

A inicialização básica de um AG consiste na formação de uma população inicial composta de indivíduos, sobre a qual serão aplicadas as ações dos passos subsequentes do processo. Os indivíduos são a unidade fundamental de um AG. É comum utilizar os termos cromossomo e mesmo genoma como um sinônimo para indivíduo. A população inicial é obtida na maioria das vezes de duas formas. Ou os indivíduos são gerados aleatoriamente ou através de uma heurística relacionada às características específicas do problema abordado. A população gerada não pode ser excessivamente pequena, pois terá pouca representatividade do espaço de busca e não pode ser excessivamente grande, uma vez que demora na convergência. Para melhorar a representatividade população inicial pode possuir indivíduos igualmente espaçados no espaço de busca.

Na geração da população, a escolha de representação para os indivíduos, também chamada de codificação, é uma etapa crítica para o desenvolvimento de um AG, visto que ela será a principal responsável para o desempenho do programa, ou seja, a codificação consiste em uma maneira de traduzir a informação do nosso problema em uma maneira viável de ser tratada pelo computador. As formas de codificação mais comuns são:

- Binário

- Binário codificando real

- Inteiro

- Real

- Vetores, listas e matrizes

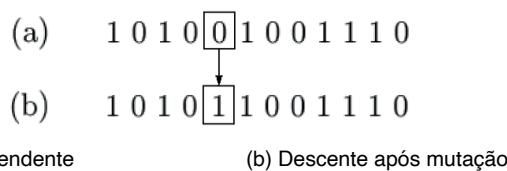

A codificação binária é a mais simples e mais usada pelos praticantes da área dos AG. Isto se deve ao fato de que geralmente as variáveis do problema trabalhado podem ser representadas em números binários. Nesta representação, cada cromossomo é uma série de bits (genes) de valores 0 ou 1. O conceito representado por cada bit ou conjunto de bits é inerente ao problema. A Figura 15 mostra exemplos de cromossomos utilizando codificação binária.

| Cromossomo A                    | Cromossomo B                  |

|---------------------------------|-------------------------------|

| 1 0 1 1 0 0 1 1 1 1 0 0 1 0 0 1 | 1 1 1 1 0 1 1 0 1 1 1 0 0 1 1 |

Figura 15 - Exemplo de cromossomo na codificação binário

Entretanto, a codificação binária possui algumas desvantagens quando é aplicada à problemas de alta dimensionalidade e com alta precisão numérica. Isto ocorre pelo fato de quando existe um grande número de variáveis, obtém-se longas cadeias de bits que podem fazer o algoritmo convergir vagarosamente, neste caso é recomendado utilizar outro tipo de codificação, tal como a codificação real.

Na codificação real, o cromossomo é representado por um vetor de números reais, no qual cada posição do vetor (gene) contém o valor de uma variável do problema. A Figura 16 mostra um cromossomo utilizando codificação real.

|      |      |      |      |      |      |      |      |      |      |      |      |      |

|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 1,29 | 0,34 | 1,04 | 1,45 | 0,89 | 0,09 | 1,03 | 1,93 | 1,12 | 1,33 | 1,01 | 0,08 | 0,11 |

|------|------|------|------|------|------|------|------|------|------|------|------|------|

Figura 16 - Exemplo de cromossomo na codificação real

## 2.2 AVALIAÇÃO (FUNÇÃO OBJETIVO OU *FITNESS*)

Nesta etapa é realizado o primeiro passo da seleção, cada indivíduo da população é avaliado para que seja determinado o seu grau de adaptação. A função de avaliação também é chamada de função objetivo ou função *fitness* em um grande número de trabalhos. Na verdade, a função de avaliação trabalha em conjunto com a escolha da codificação.

A função de avaliação é o ponto do algoritmo mais dependente do problema em si. É necessário aqui que o AG seja capaz de responder sobre quão boa uma resposta é para o problema proposto. A função objetivo toma como entrada um cromossomo e retorna um número, ou uma lista de números, que representam o desempenho do cromossomo com

relação a como o mesmo auxilia na resolução do problema. Um exemplo de função objetivo é apresentado a seguir. Neste caso, deseja-se buscar do valor máximo da função:

$$f(x) = x^3 - x^2 - 10x \quad (1)$$

O valor de retorno da função *fitness* é dado por:

$$fo(C) = f(d(C)) \quad (2)$$

Onde  $fo(C)$  é a função *fitness* aplicada sobre o cromossomo C;  $d(C)$  a função que decodifica os genes do cromossomo em um valor x.

Se  $C = [0001010100101001]$  e  $d(x)$  é uma função que decodifica números binários em reais, então:  $d(C) = 17,2337$ ;  $f(d(C)) = 361,131$ . Logo,  $fo(C) = 361,131$ .

Várias formas de avaliação são utilizadas atualmente, em casos de otimização de funções matemáticas, o próprio valor de retorno destas tende a ser escolhido, e em problemas com muitas restrições, funções baseadas em penalidades são mais comuns. Em muitos casos, calcular com exatidão completa o grau de adaptação dos indivíduos pode ser uma tarefa complexa, e se levarmos em conta que esta operação é massivamente repetida ao longo do processo de evolução, seu custo pode ser consideravelmente alto. Em tais situações é comum o uso de funções não determinísticas, que não avaliam a totalidade das características do indivíduo, operando apenas sobre uma amostragem destas.

## 2.3 SELEÇÃO

A função de seleção em um AG é escolher os elementos da população que participarão do processo de reprodução, isto é, selecionar os pais dos indivíduos que estarão presentes na nova população. Esta escolha deve ser feita de tal forma que os membros da população mais adaptados, tenham maior chance de reprodução, isto é, àqueles que apresentam um valor da função objetivo mais elevado.

Caso não houvesse o processo de seleção, além do AG perder a grande parte do caráter evolutivo, o mesmo seria um processo ineficiente, similar a uma busca aleatória. Existem várias formas para efetuar a seleção, porém não existe um senso comum em relação a qual método é melhor para determinado tipo de problema, isto ainda é uma questão aberta em AG (MITCHELL, 1999). Nos itens a seguir são apresentados os principais métodos de seleção.

### 2.3.1 Seleção por torneio

Neste método são aleatoriamente escolhidos grupos de cromossomos de tamanho  $n$ , com probabilidade de escolha igual. O cromossomo com maior valor na função *fitness* é selecionado para gerar descendentes. Os valores comumente utilizados são de  $n = 2$  ou  $n = 3$ .

### 2.3.2 Seleção uniforme

Neste método todos os indivíduos possuem a mesma probabilidade de serem selecionados. Obviamente, esta forma de seleção possui uma probabilidade muito remota de causar uma melhora da população sobre a qual atua.

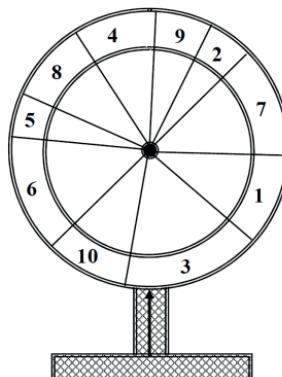

### 2.3.3 Seleção da roleta

É o método mais utilizado, cujo objetivo é selecionar indivíduos aleatoriamente, proporcionando mais chances de reprodução aos indivíduos mais aptos da população. O método de seleção da roleta funciona da seguinte forma:

- calcula-se o somatório da adequação da população (total);

- sorteia-se um valor aleatório  $i$  tal que pertence ao intervalo  $[0; \text{total}]$ ;

- seleciona-se o indivíduo  $x$  tal que a ele corresponda a faixa do somatório onde  $i$  se localiza;

A Figura 17 mostra um exemplo de seleção aplicando o método da roleta

| CROMOSSOMO | 1 | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

|------------|---|----|----|----|----|----|----|----|----|----|

| APTIDÃO    | 8 | 2  | 17 | 7  | 2  | 12 | 11 | 7  | 3  | 7  |

| $\sum A_i$ | 8 | 10 | 27 | 34 | 36 | 48 | 59 | 66 | 69 | 76 |

Rodando a roleta:

|                        |    |    |    |    |   |    |    |

|------------------------|----|----|----|----|---|----|----|

| NÚMERO ALEATÓRIO       | 23 | 49 | 76 | 13 | 1 | 27 | 57 |

| CROMOSSOMA SELECIONADO | 3  | 7  | 10 | 3  | 1 | 3  | 7  |

Figura 17 - Método da roleta usado para seleção em AG (SOUZA, 2013)

### 2.3.4 Seleção por ranking

Este método evita a convergência prematura e a dominância de “super indivíduos” que possuem um valor alto de aptidão em relação à média da população. Seu princípio consiste em:

- ordenar todos os elementos de acordo com a sua função objetivo;

- usar este *ranking* como base da seleção;

- não usar diretamente o valor da função objetivo.

Destaca-se que o passo de ordenação é extremamente oneroso em termos de tempo. Uma vez estabelecido o *ranking*, deve-se fazer o seu mapeamento para uma função *fitness*. Feito o mapeamento, emprega-se qualquer outro método visto anteriormente.

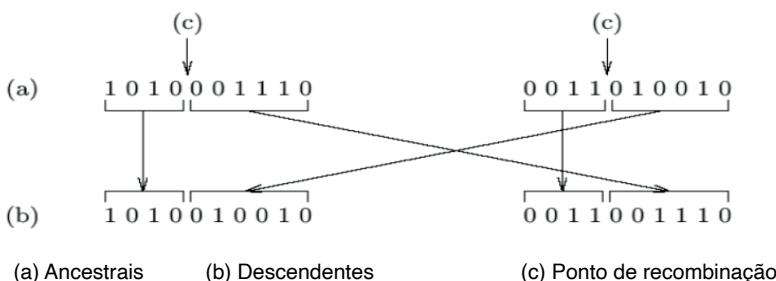

## 2.4 CRUZAMENTO (RECOMBINAÇÃO)

O cruzamento é o operador responsável pela recombinação de características dos pais durante a reprodução, permitindo que as próximas gerações herdem essas características. O cruzamento cria novos cromossomos, os quais são chamados de descendentes, para a população através da recombinação de partes diferentes de cromossomos-pai escolhidos através do método de seleção. Diferentes operadores de cruzamento têm sido apresentados na literatura, a escolha de qual aplicar é dependente principalmente do tipo de codificação escolhida. Os itens a seguir apresentam algumas técnicas de cruzamento para geração de novos cromossomos.

### 2.4.1 Cruzamento em um ponto

O cruzamento em um ponto consiste em dividir os cromossomos selecionados num ponto de sua cadeia, onde este ponto é escolhido aleatoriamente. Após isso, copiamos uma parte dos cromossomos de cada pai, para gerar os cromossomos dos novos filhos. É comum neste operador de cruzamento, os pais gerarem dois novos filhos, mas pode-se criar qualquer quantidade de filhos, desde que, o número de alelos permita o número desejado de combinações diferentes. A Figura 18 a seguir demonstra um exemplo de cruzamento de um ponto para codificação binária.

Figura 18 - Cruzamento de um ponto (STEMMER, 2013)

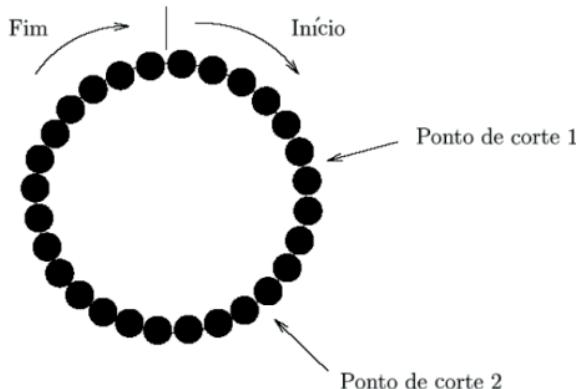

## 2.4.2 Cruzamento multipontos

Neste operador os cromossomos são vistos como anéis com início e fim unidos. Escolhem-se dois pontos de ruptura do anel e o trecho entre estes pontos é substituído. Padrões são rompidos proporcionalmente ao seu comprimento de definição. O princípio do operador de cruzamento multiponto é mostrado na Figura 19.

Figura 19 - Técnica de cruzamento multipontos (STEMMER, 2013)

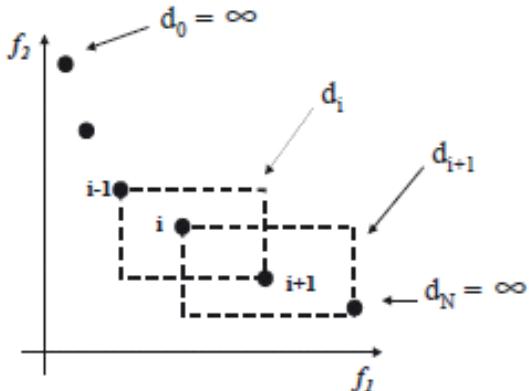

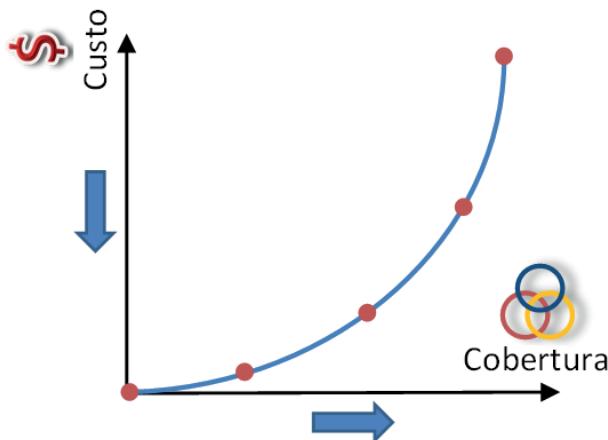

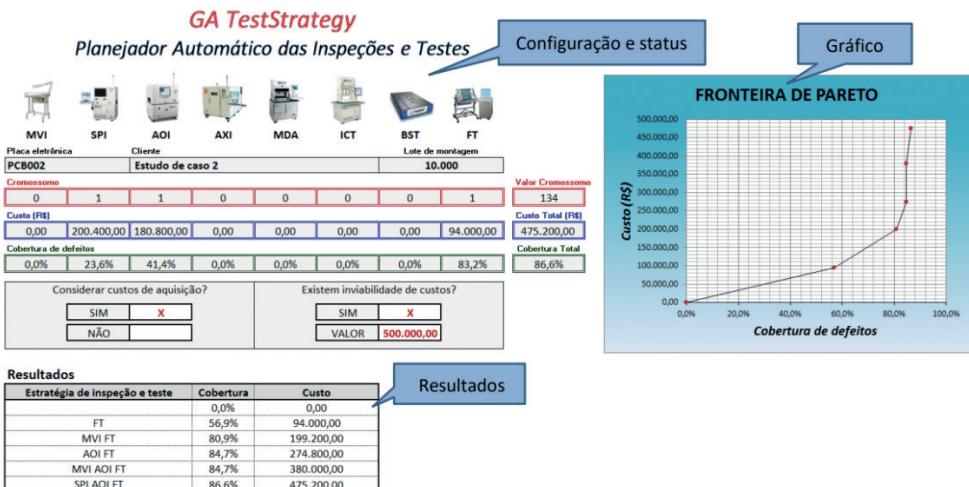

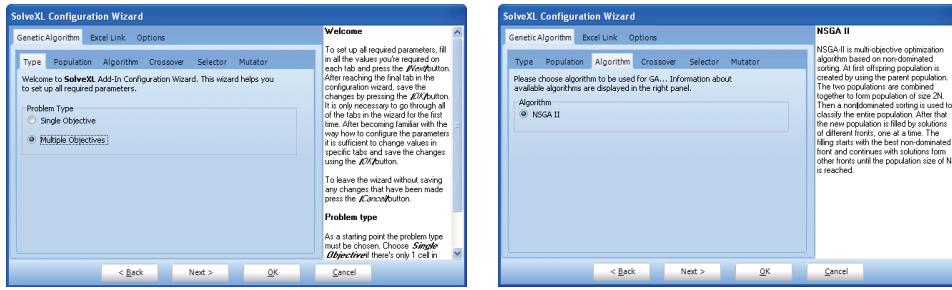

## 2.4.3 Cruzamento Uniforme